FPGAで自作CPUを動かしてみよう (1)

この記事はIS17er advent calendar と TSG advent calendar の15日目の記事として書かれました。cookies146、お誕生日おめでとうございます。これは、お誕生日プレゼントを作ろうとする試みです。

FPGAでCPUを動かすことについて、ISの先輩の記事などから断片的な知識は得られるのですが設計など全く分からない初心者が全体像を把握したいような時に読める記事が無かったので書きました。間違いがあったら指摘してください。

いつになるか分かりませんが一応続くつもりです。

今日の話は、物理的に必要なもの(購入が必要なもの)と漠然とした設計の話です。

とりあえず、必要なもの

・FPGAスーパーキット(これがないと始まらない)

・ MAX10-FB基板用の追加部品

・発振器

・ピンヘッダ2*40

・ピンヘッダ1*40

・ピンソケット1*40

・ピンソケット2*20

・ジャンパピン

・SDRAM(オプション)

・MAX10-JB基板用の追加部品

・PICマイコン

・レギュレータ

・LED緑

・LED黄

・ポリスイッチ

・水晶発振子

・抵抗の中から120,130,10k,10k,2,2kΩ

・電解コンデンサ*2

・積層コンデンサ0.1μF

・積層コンデンサ22pF

・USBコネクタ

その他

環境構築

スーパーキットの本に従って、基盤の組み立てとQuartusの導入、FPGAでLチカくらいまでしましょう。(所要時間10時間)

良ければこの記事を参考にして下さい。

設計の雰囲気

お手本にするアーキテクチャはMC6800で、一応先行研究としてこんなブログを発見したが、途中で途切れているのでネタの被りはなかったことにします。この記事だって途中で途切れるかもしれないし。MC6800にしたのは8bitCPUが作りたいとハードウェアの先生に相談したところ、おすすめされたため。

具体的な話は今度にして、とりあえず何を作って何を作らないかを明確にする。

イメージ的にはこんな感じ。RAMとROMはQuartusのwizardという機能でサクッと作れるので、実際にHDLを書くのはcontrolerとALUになる。

現在CPUのモードを3つ考えている。

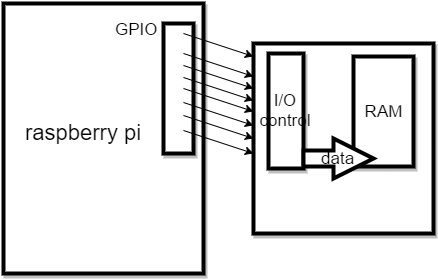

1.ラズパイのGPIOから信号を受け取りRAMの開始番地から書き込む

2.RAMから命令をfetchし、実行する

3.実行結果をラズパイに送る

1,3は外部と通信するとそれっぽいかなというだけで、本質的には2が重要である。

1のイメージ図

ラズパイのGPIOからの通信をFPGAの外部ピンで受信し、I/O controlerを介して命令がRAMに書き込まれる。

2のイメージ図

RAMから命令がfetchされ、Decodeされてexecuteされるよ、という図。

今回はここまで。

次回はタイムチャートとブロック構成と入出力を決めたい。